#### The study and characterisation of High-Flux CdZnTe using

**Ben Cline**

Detector Development Group, UKRI STFC Email: <u>ben.cline@stfc.ac.uk</u>

20/09/2023

Detector **Development Ivan Church Ben Cline** Matt Hart Sion Richards **Paul Seller Dave Sole** Matt Wilson **Rhian Wheater** Matt Veale

**Interconnect Paul Adkin Paul Booker Toby Brookes** Navid Ghorbanian John Lipp **Andreas Schneider**

**Detector Systems** Software **Dominic Banks Victor Bozhinov Adam Davies Josh Harris Ashley Neaves Tim Nicholls Joseph Nobes** HEXITEC

Funded by the: Centre for Instrumentation (CFI) run by Marcus French

**PCB Design Office Darren Ballard Dan Becket Chris Day**

**ASIC Design Stephen Bell Thomas Gardiner** Lawrence Jones Mark Prydderch

#### **Detector Systems** William Helsby

**Electronic Systems** Design Adam Barcock **Rob Halsall** John Holden **Chris Lyford** Sooraj Pradeep **Matt Roberts**

## **1 HEXITEC vs HEXITEC**<sub>MHz</sub>

The next generation of HEXITEC systems

## 2 HEXITEC<sub>MHz</sub> Overview

An introduction to our new  $\text{HEXITEC}_{\text{MHz}}$  ASIC including its architecture and specification

#### **3 HF-CZT Test Results**

Characterisation of spectroscopic performance using a labbased X-Ray source and Diamond Light Source synchrotron X-Rays

### **4 Next Steps**

A look to the next 12 months

## Agenda

## **1 HEXITEC vs HEXITEC**<sub>MHz</sub>

The next generation of HEXITEC systems

## 2 HEXITEC<sub>MHz</sub> Overview

An introduction to our new HEXITEC<sub>MHz</sub> ASIC including its architecture and specification

### **3 HF-CZT Test Results**

Characterisation of spectroscopic performance using a labbased X-Ray source and Diamond Light Source synchrotron X-Rays

### **4 Next Steps**

A look to the next 12 months

- Fully spectroscopic X-Ray Imaging with CdTe/ CdZnTe (CZT) detectors

- $80 \times 80$  pixel array on a 250  $\mu m$  pitch

- Analogue readout via a rolling shutter to 4 ADCs in the DAQ

- Maximum ~10 kHz data output (~100 MB s<sup>-1</sup>)

- AMS 0.35 μm since 2010

**HEXITEC** specifications

| Parameter                                                        | HEXITEC                                                                                                                             |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Pixel Pitch (µm)                                                 | 250                                                                                                                                 |

| Array Size                                                       | 80 × 80                                                                                                                             |

| Max Frame Rate (kHz)                                             | ~10                                                                                                                                 |

| Max Spectroscopic Flux<br>(ph s <sup>-1</sup> mm <sup>-2</sup> ) | ~10 <sup>4</sup>                                                                                                                    |

| Digitisation                                                     | Off-chip                                                                                                                            |

| Detector Type                                                    | Peak Track + Hold                                                                                                                   |

| Gain stages (keV in CZT)                                         | 200                                                                                                                                 |

|                                                                  | 600                                                                                                                                 |

| FWHM <sub>@100keV</sub> (keV in CZT)                             | <1 <ul> <li>HF-CZT: 0.79 keV</li> <li>@ 59.54 keV [1]</li> <li>300-µm thick p-type Si: 0.59 keV</li> <li>@ 59.54 keV [2]</li> </ul> |

[1] DOI: 10.3390/s20102747 [2] DOI: 10.1088/1748-0221/17/05/P05030

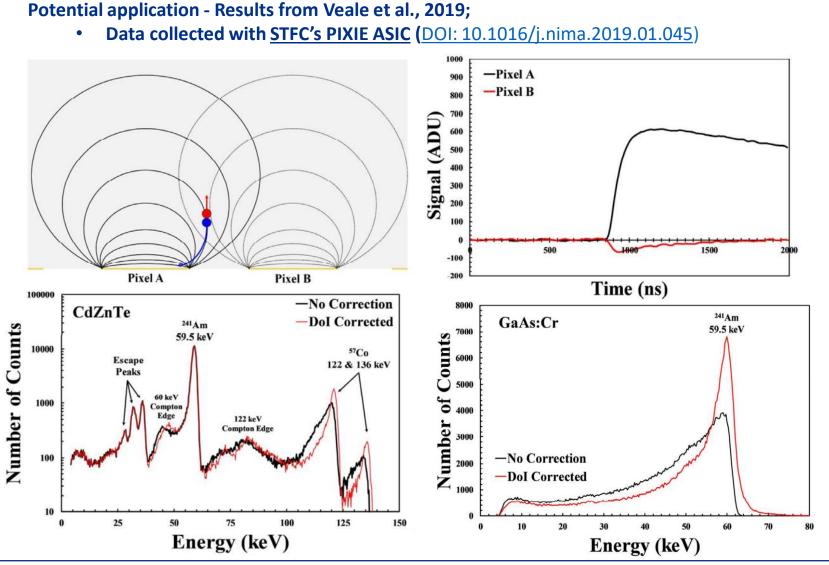

• HEXITEC has been used across many applications including:

#### X-Ray Fluorescence Imaging [4]

Figure 7. (a) Pt and Er XRF intensity maps as a function of temperature during the solidification of an Al-23Pt-20Er alloy at 0.1  $\rm Ks^{-1}.$

#### Hyperspectral X-Ray Tomography [5]

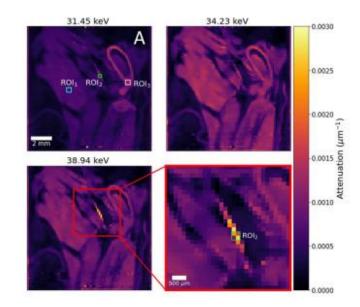

**Figure 2.** Voxel spectra analysis for double-stained hindlimb specimen. (A) Single image slice in the sagittal plane across three monochromatic energy channels, following iterative reconstruction. A set of three regions-ofinterest (ROIs) are highlighted for voxel spectra analysis.

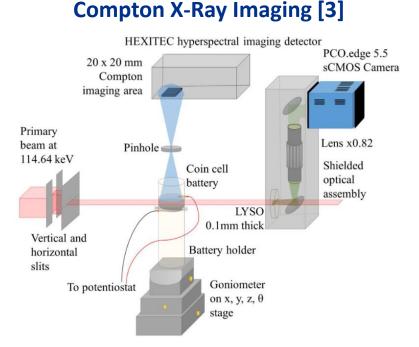

Figure 1. Schematic of the correlative X-Ray Compton scattering imaging (XCS-I) and X-Ray computed tomography (XCT) technique experimental set-up

#### [3] DOI: 10.1016/j.mtener.2022.101224 [4] DOI: 10.1557/mrs.2020.270 [5] DOI: 10.1038/s41598-022-23592-0

6 of 35

### BUT ...

#### • HEXITEC is frame-rate and therefore flux limited

- Charge-sharing corrections require <10 % frame occupancy

- This limits spectroscopic imaging @10 kHz to a max X-Ray flux of ~10<sup>4</sup> ph s<sup>-1</sup> mm<sup>-2</sup>

→ There is a need for a continuous spectroscopic X-Ray detector that operates at faster frame rates

- Faster (MHz) imaging requires:

- In-pixel digitisation

- High-speed serialisers

- Dedicated FPGA processing

- These requirements apply to a large number of STFC's upcoming detector development projects

- E.g. DynamiX, C100

# HEXITEC

A new fully spectroscopic X-Ray imaging detector:

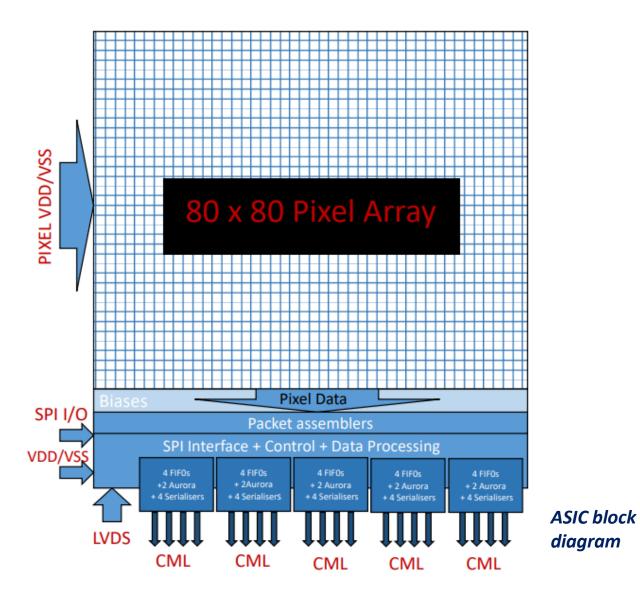

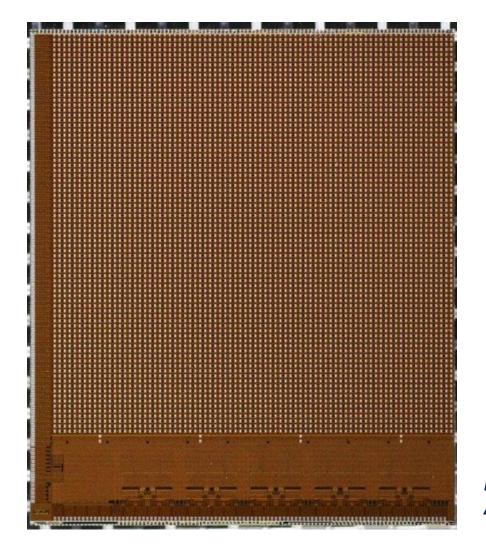

- 80  $\times$  80 pixels on a 250  $\mu$ m pitch

- New front-end design now an **integrating** detector

- On-chip 12-bit digitisation (no external ADCs)

- Data outputted via 20 × 4.1 Gbps serialisers

- 1 MHz continuous frame rate

- Spectroscopic X-Ray fluxes of >10<sup>6</sup> ph s<sup>-1</sup> mm<sup>-2</sup>

Facilities Council

#### Comparison of HEXITEC and HEXITEC<sub>MH2</sub> specifications

| Parameter                                                        | HEXITEC          | HEXITEC <sub>MHz</sub>   |

|------------------------------------------------------------------|------------------|--------------------------|

| Pixel Pitch (μm)                                                 | 250              | 250                      |

| Array Size                                                       | 80 × 80          | 80 × 80                  |

| Max Frame Rate (kHz)                                             | ~10              | 1000                     |

| Max Spectroscopic Flux<br>(ph s <sup>-1</sup> mm <sup>-2</sup> ) | ~10 <sup>4</sup> | > <b>10</b> <sup>6</sup> |

| Digitisation                                                     | Off-chip         | On-chip                  |

| Detector Type                                                    | Track + Hold     | Integrating              |

| Gain Stages (keV in CZT)                                         | 200              | 100                      |

|                                                                  | 600              | 200                      |

|                                                                  |                  | 300                      |

| FWHM@100keV (keV in CZT)                                         | <1               | <1                       |

| Power Consumption (W)                                            | 1.5              | 15                       |

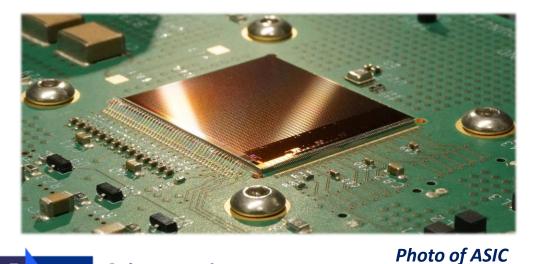

HEXITEC<sub>MHz</sub> ASIC

### **1 HEXITEC vs HEXITEC**<sub>MHz</sub>

The next generation of HEXITEC systems

## 2 HEXITEC<sub>MHz</sub> Overview

An introduction to our new  $\text{HEXITEC}_{\text{MHz}}$  ASIC including its architecture and specification

#### **3 HF-CZT Test Results**

Characterisation of spectroscopic performance using a labbased X-Ray source and Diamond Light Source synchrotron X-Rays

#### **4 Next Steps**

A look to the next 12 months

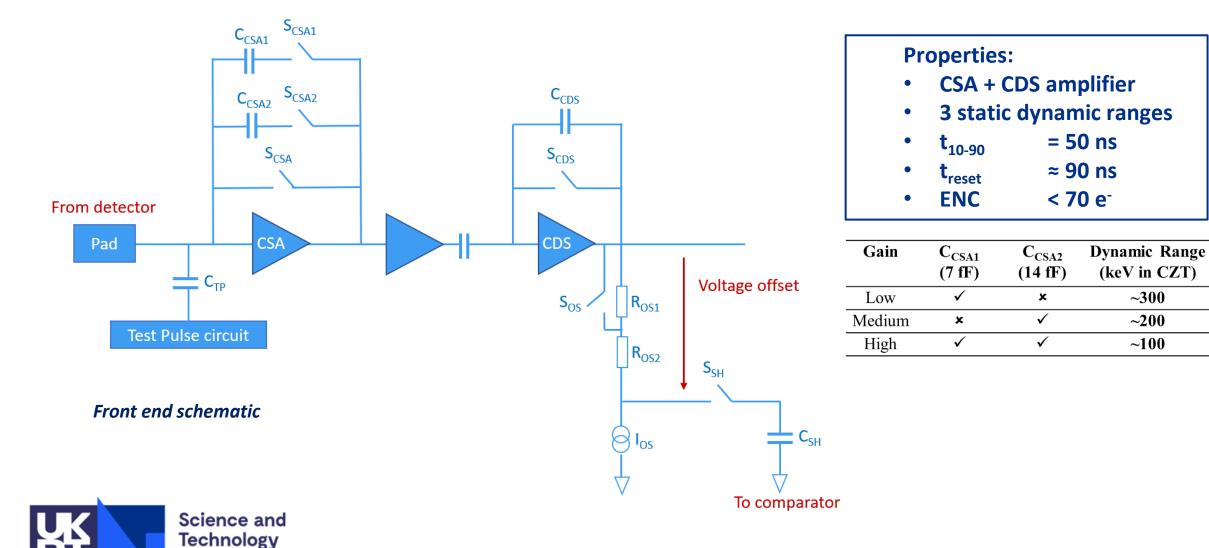

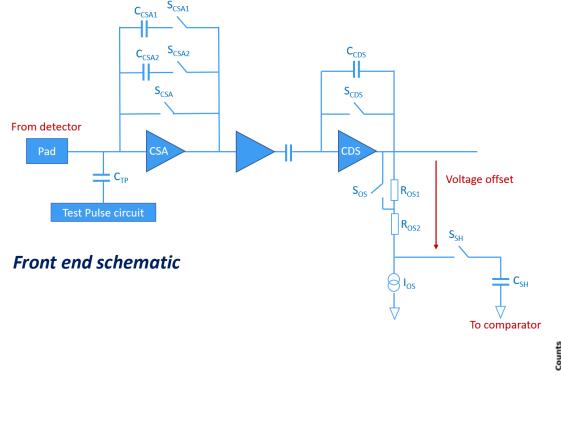

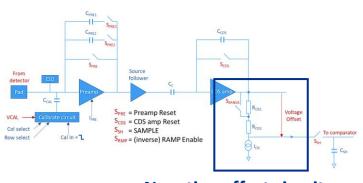

# **HEXITEC<sub>MHz</sub>** - Integrating Front End

**Facilities** Council

(keV in CZT)

~300

~200

~100

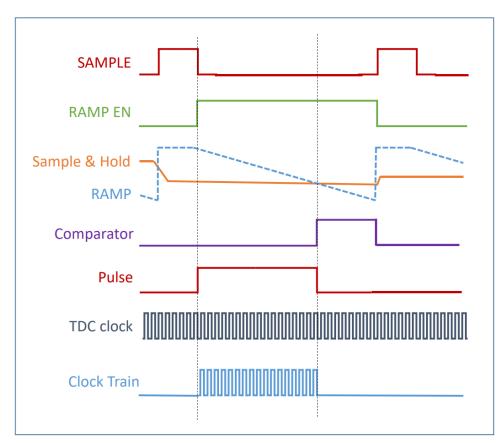

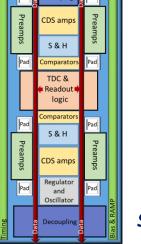

# **HEXITEC**<sub>MHz</sub> - In-Pixel TDC

#### TDC signal timing

- 12-bit digitisation

- The Sample & Hold signal is compared with a ramp with a programmable slew

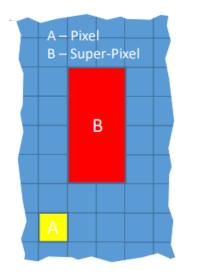

- The ASIC comprises 800 super-pixels of 2 × 4 pixels

- These contain one TDC block and shared readout logic

Super-pixel schematics

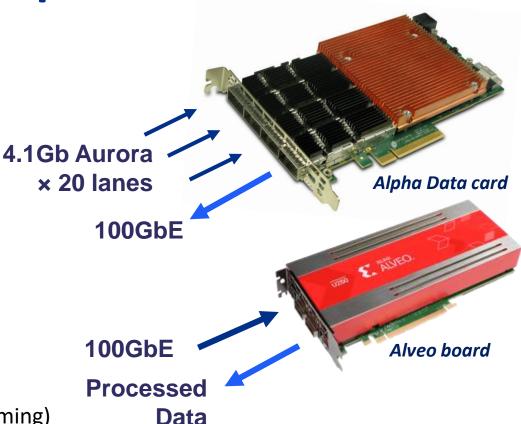

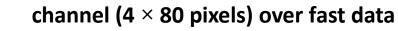

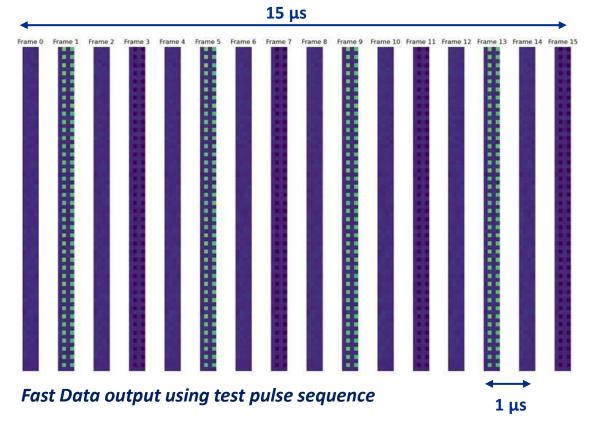

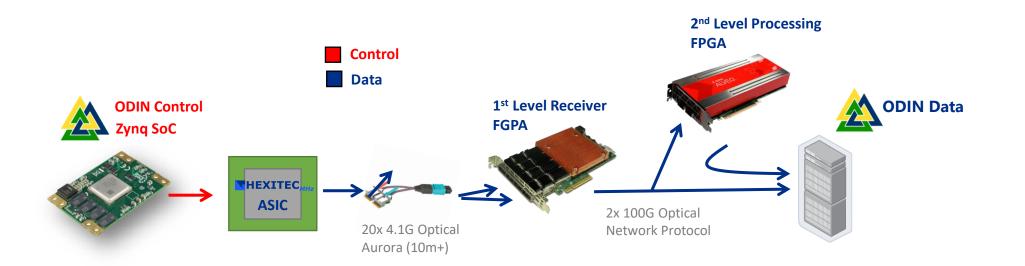

# **HEXITEC**<sub>MHz</sub> - Data Output

- + 80  $\times$  80 array is divided into divisions of 4 columns

- Each division has packet-assembler and dedicated serialiser

- Packets constructed using Xilinx's Aurora 64B/66B protocol

- Serialisers operate at 4.1 Gb s<sup>-1</sup> (total data rate ≈ 10 GBs<sup>-1</sup>)

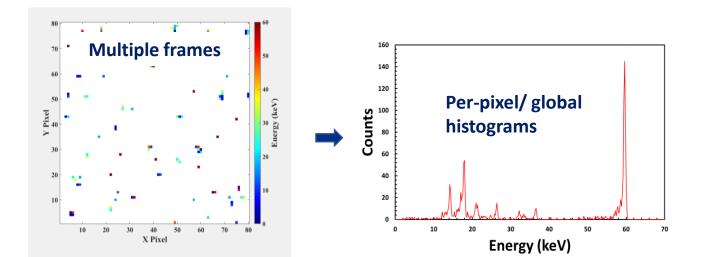

#### What to do with all this data?

- Two receiving data planes:

- First-stage FPGA Alpha Data card

- Recovers and reorders the received optical data

- Second-stage FPGA Xilinx Alveo U50 board

- Data corrections (darks, energy calibration)

- Data reduction (charge-sharing discrimination, histogramming)

- Then received by ODIN Data, a scalable data-processing and acquisition network

# HEXITEC<sub>MHz</sub> - Data Output

• Then received by ODIN Data, a scalable data-processing and acquisition network

## Agenda

## **1 HEXITEC vs HEXITEC**<sub>MHz</sub>

The next generation of HEXITEC systems

## 2 HEXITEC<sub>MHz</sub> Overview

An introduction to our new HEXITEC<sub>MHz</sub> ASIC including its architecture and specification

#### **3 HF-CZT Test Results**

Characterisation of spectroscopic performance using a labbased X-Ray source and Diamond Light Source synchrotron X-Rays

### **4 Next Steps**

A look to the next 12 months

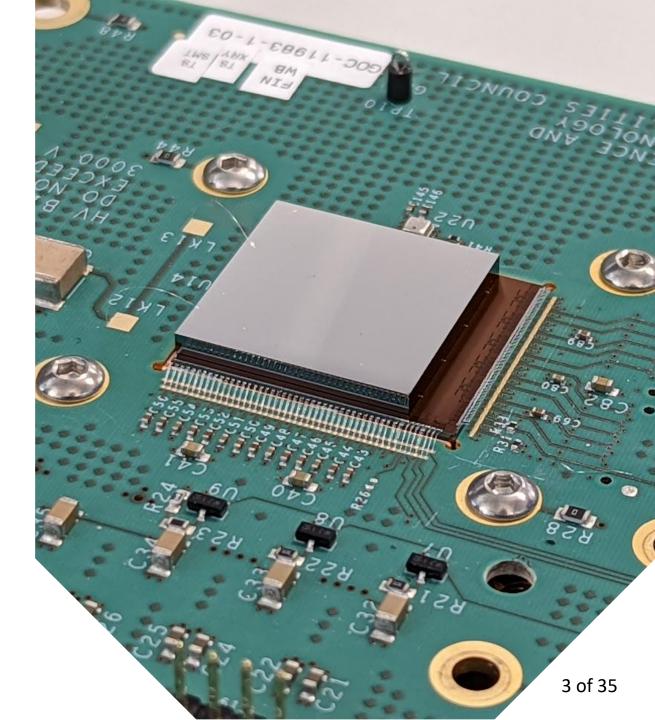

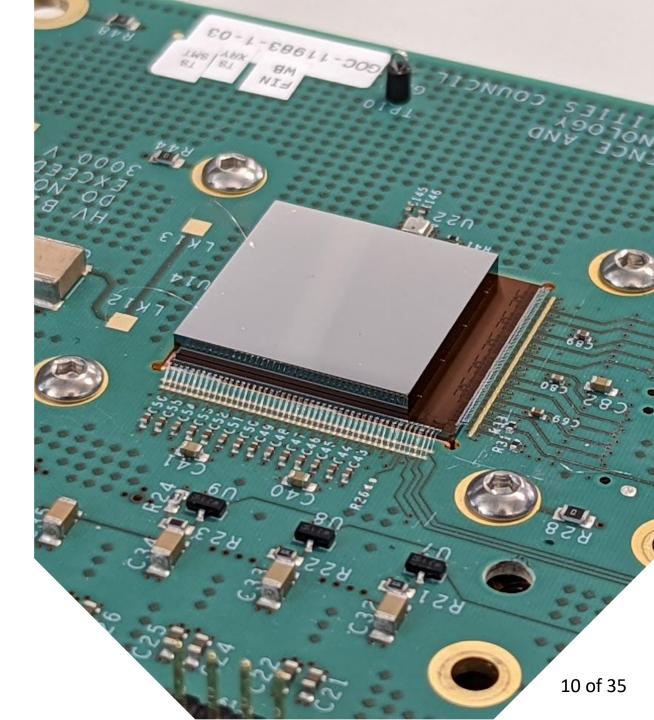

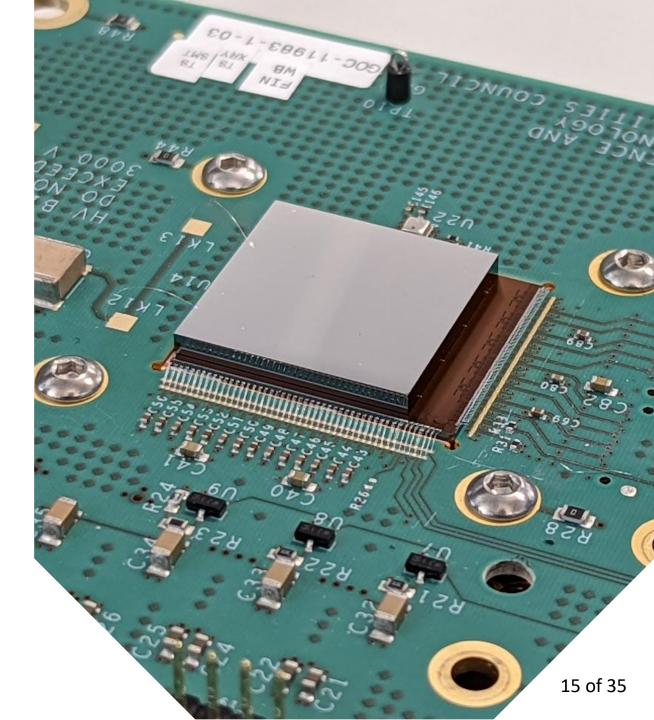

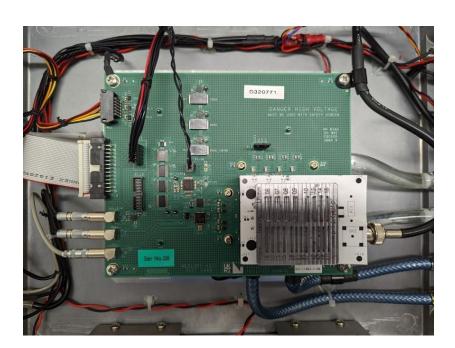

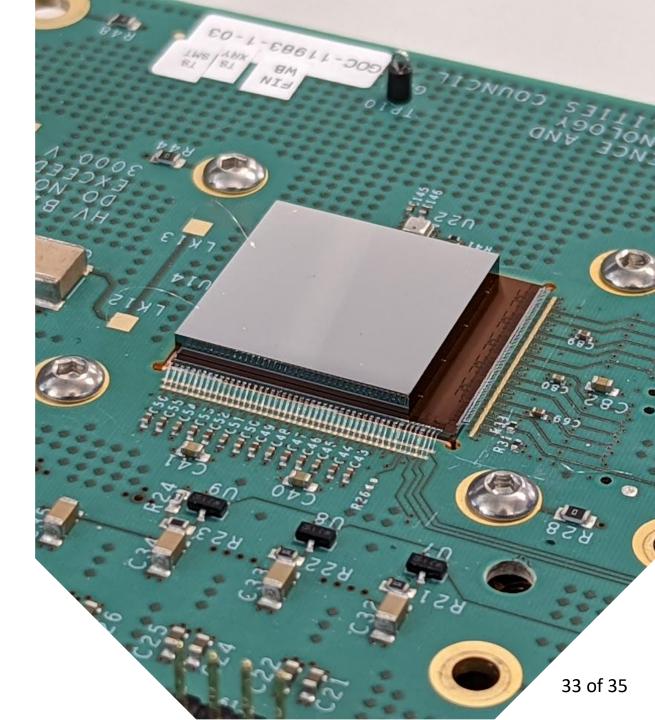

## **Current Status**

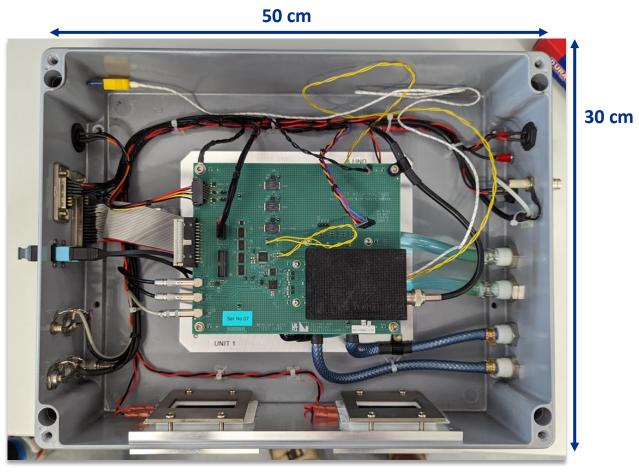

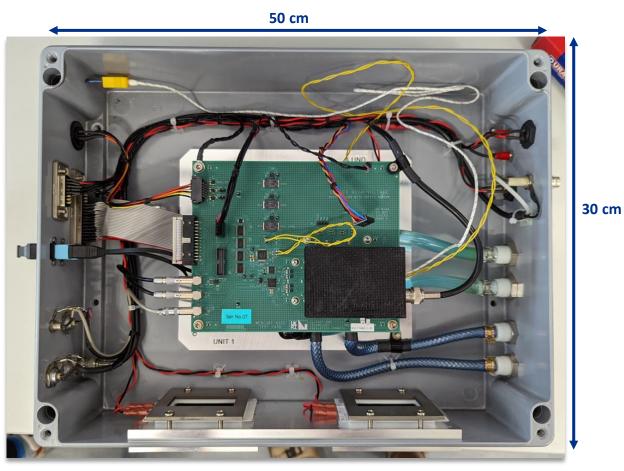

*HEXITEC*<sub>MHz</sub> test enclosure

- ASIC is fully functioning

- Using test enclosure

- FPGA firmware in development at present, 1

## **Testing – Initial X-Ray Tests**

Science and Technology

**Facilities Council**

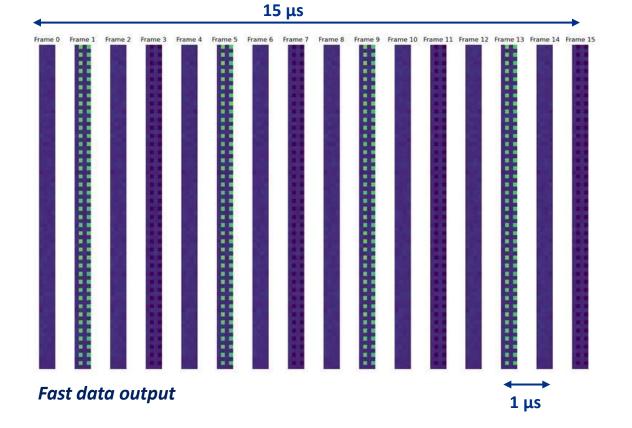

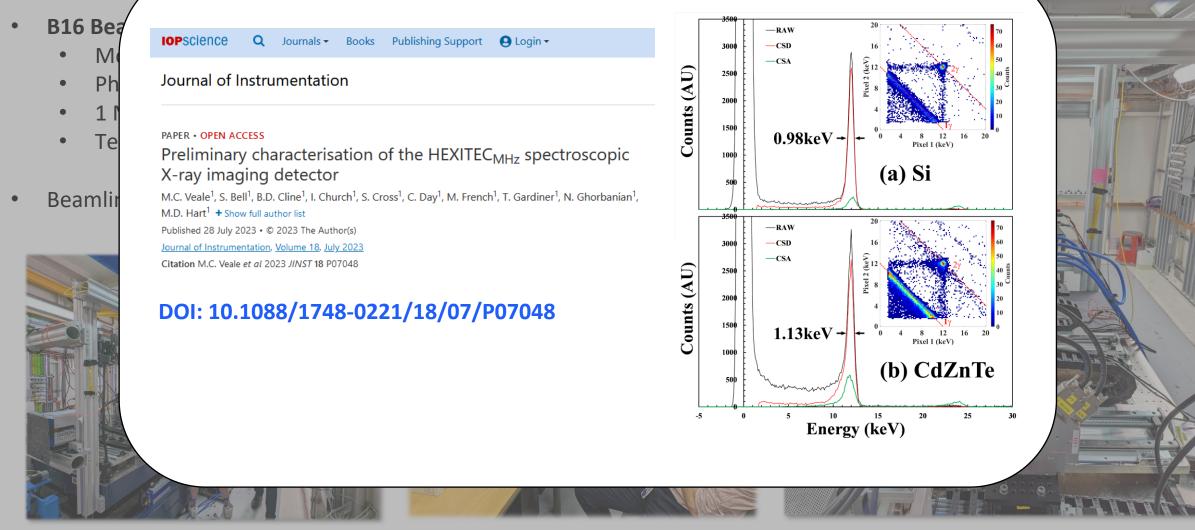

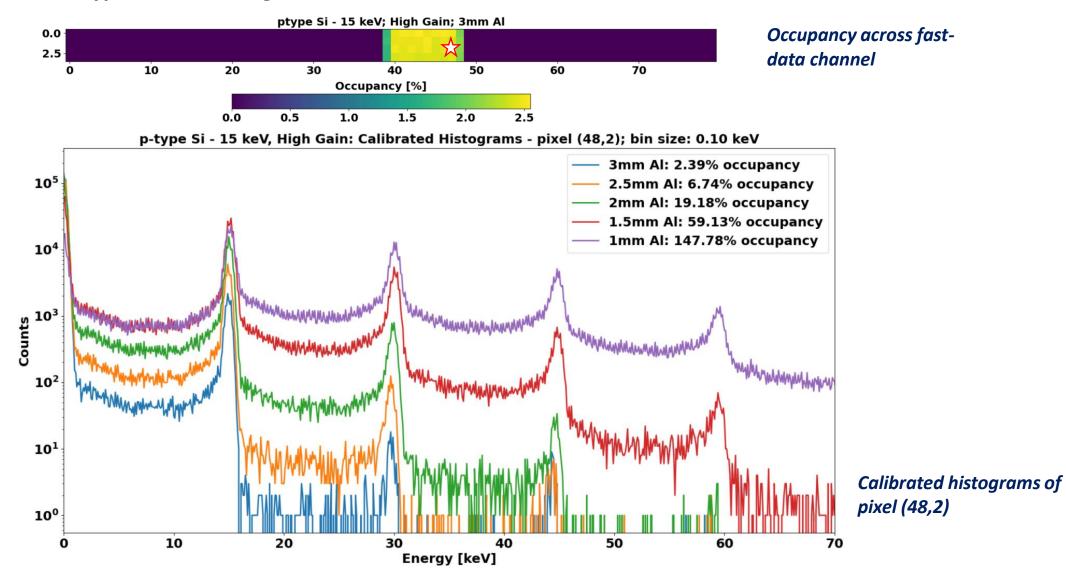

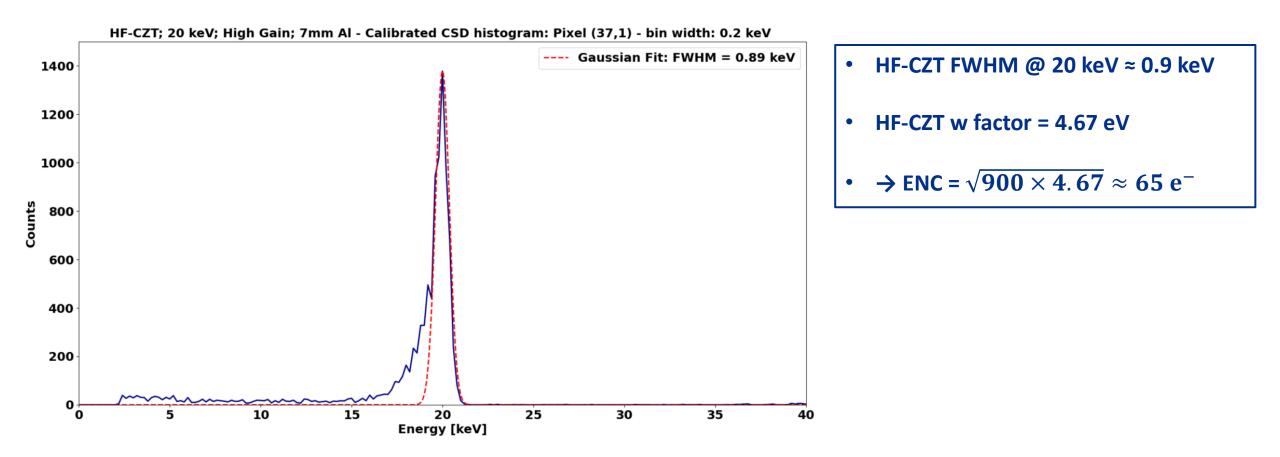

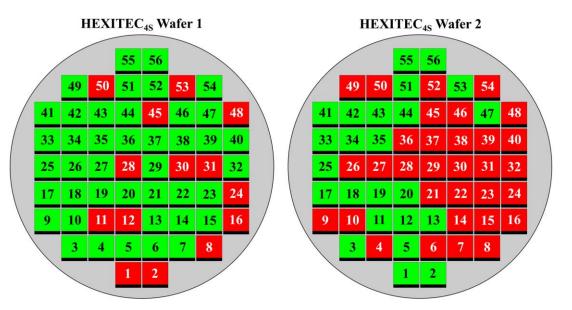

X-Ray Fluorescence (XRF) measurements of Ta foil using a  $HEXITEC_{MHz}$  HF-CZT sensor in medium-gain mode

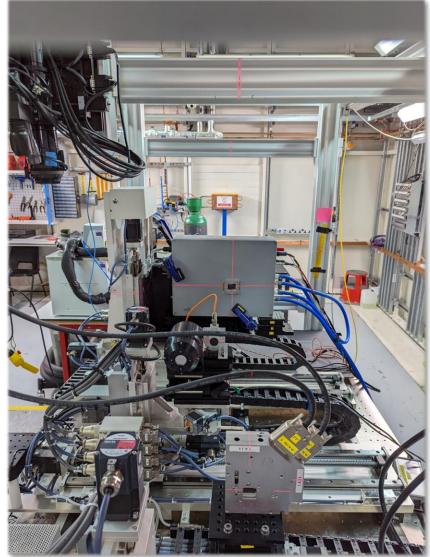

- B16 Beamline: August and December 2022

- Monochromatic X-Rays: 10 20 keV

- Photon fluxes: **10**<sup>5</sup> **10**<sup>8</sup> **ph s**<sup>-1</sup> **mm**<sup>-2</sup>

- 1 MHz data stream on one fast-data channel

- Tested HF-CZT (2 mm), p-type Si (300 μm), GaAs (500 μm) devices

- Beamline scientists: Vishal Dhamgaye, Oliver Fox, Kawal Sawhney

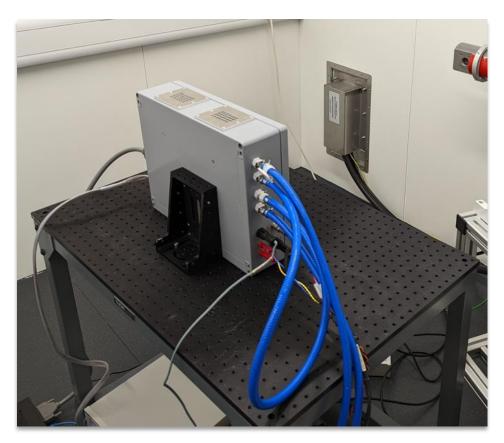

# Experimentation at diamond

**B16** setup photos

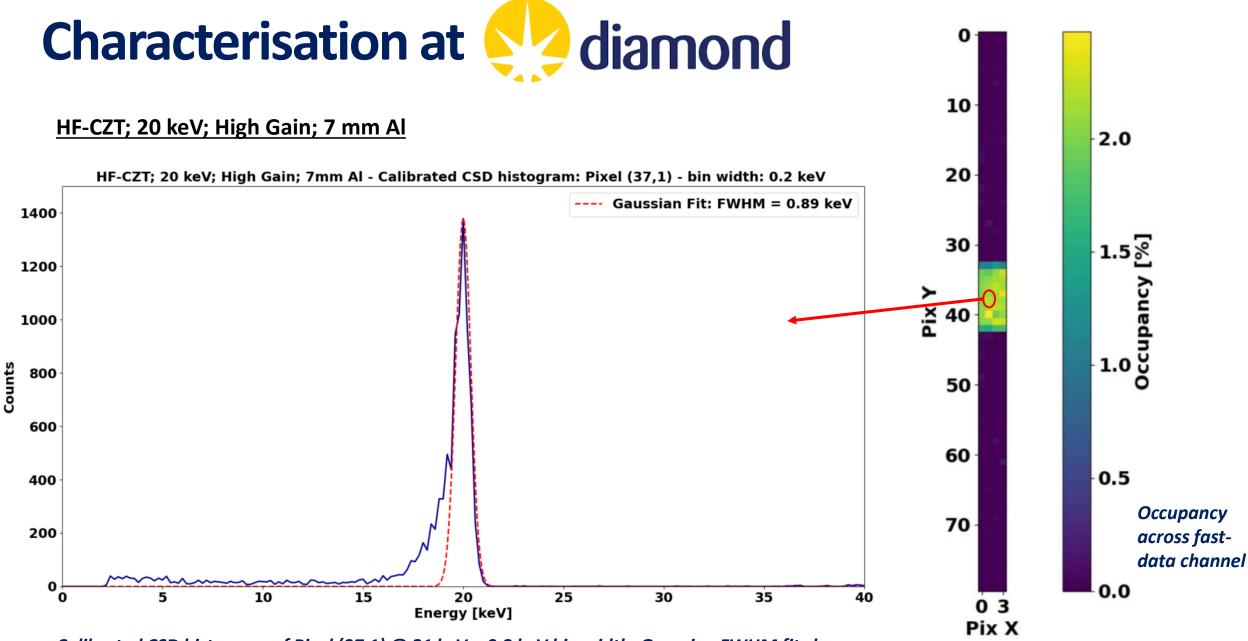

Calibrated CSD histogram of Pixel (37,1) @ 21 keV – 0.2 keV bin width. Gaussian FWHM fit shown

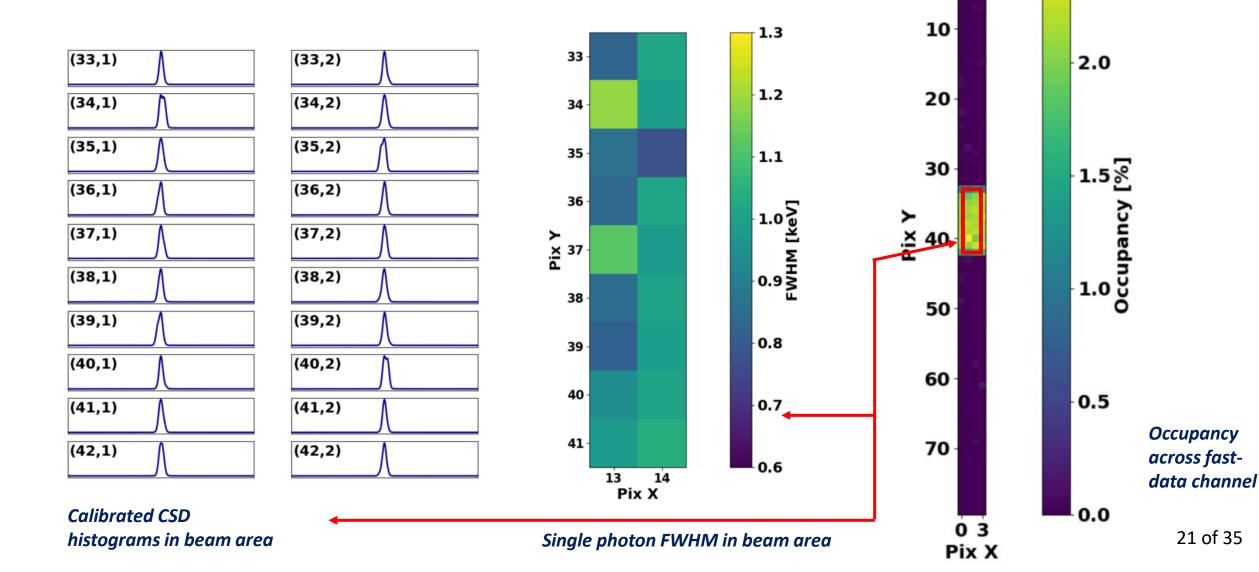

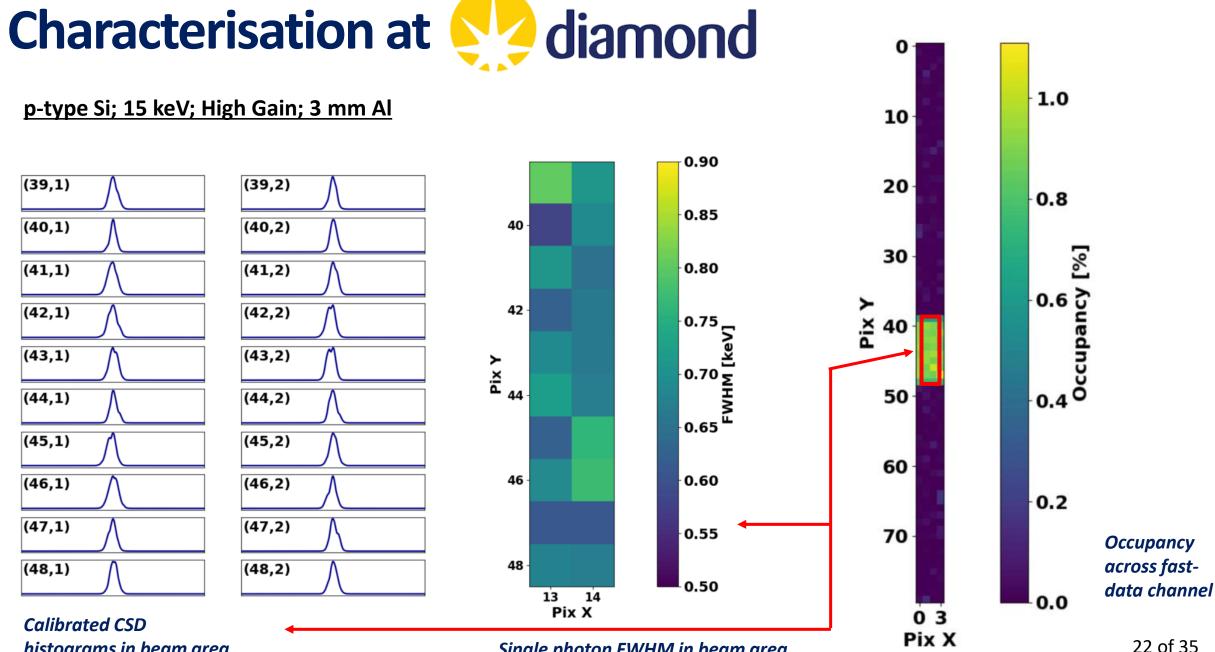

Characterisation at **diamond**

0

histograms in beam area

Single photon FWHM in beam area

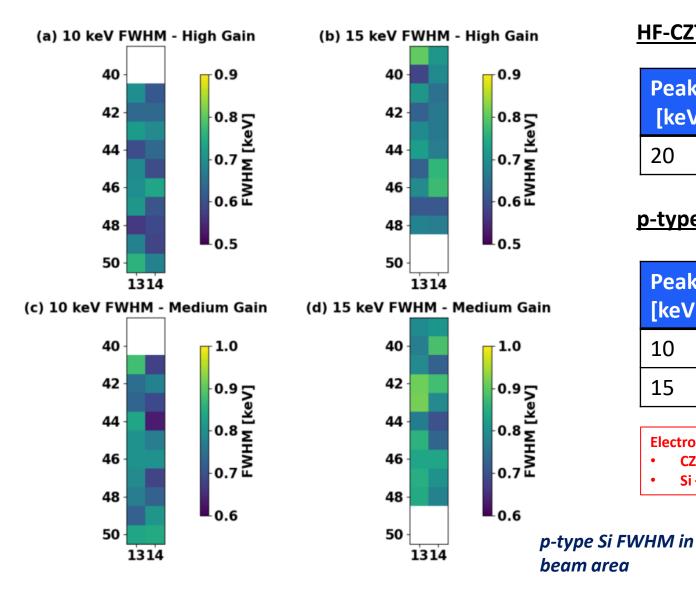

**Characterisation at diamond**

#### **HF-CZT**

| Peak Energy | HG FWHM     | MG FWHM         | LG FWHM     |

|-------------|-------------|-----------------|-------------|

| [keV]       | [keV]       | [keV]           | [keV]       |

| 20          | 0.85 ± 0.10 | $0.92 \pm 0.11$ | 1.13 ± 0.12 |

#### <u>p-type Si</u>

| Peak Energy<br>[keV] | HG FWHM<br>[keV] | MG FWHM<br>[keV] |

|----------------------|------------------|------------------|

| 10                   | 0.66 ± 0.06      | 0.77 ± 0.06      |

| 15                   | 0.68 ± 0.06      | $0.81 \pm 0.06$  |

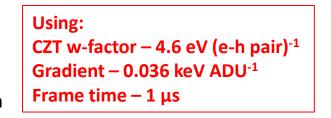

**Electron-hole pair generation energies**

CZT – 4.6 eV (e-h pair)<sup>-1</sup> .

Si – 3.6 eV (e-h pair)<sup>-1</sup>

P-type Si; 15 keV; High Gain; 3 mm Al – 0 mm Al

24 of 35

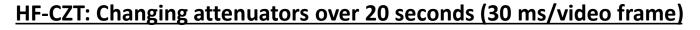

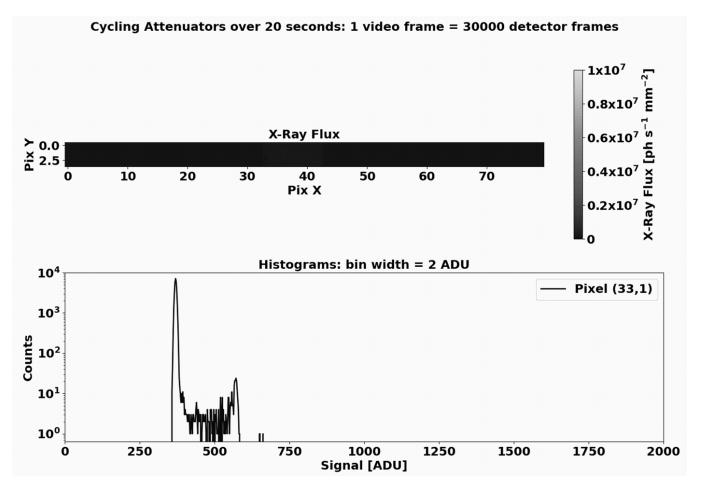

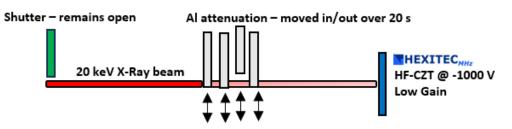

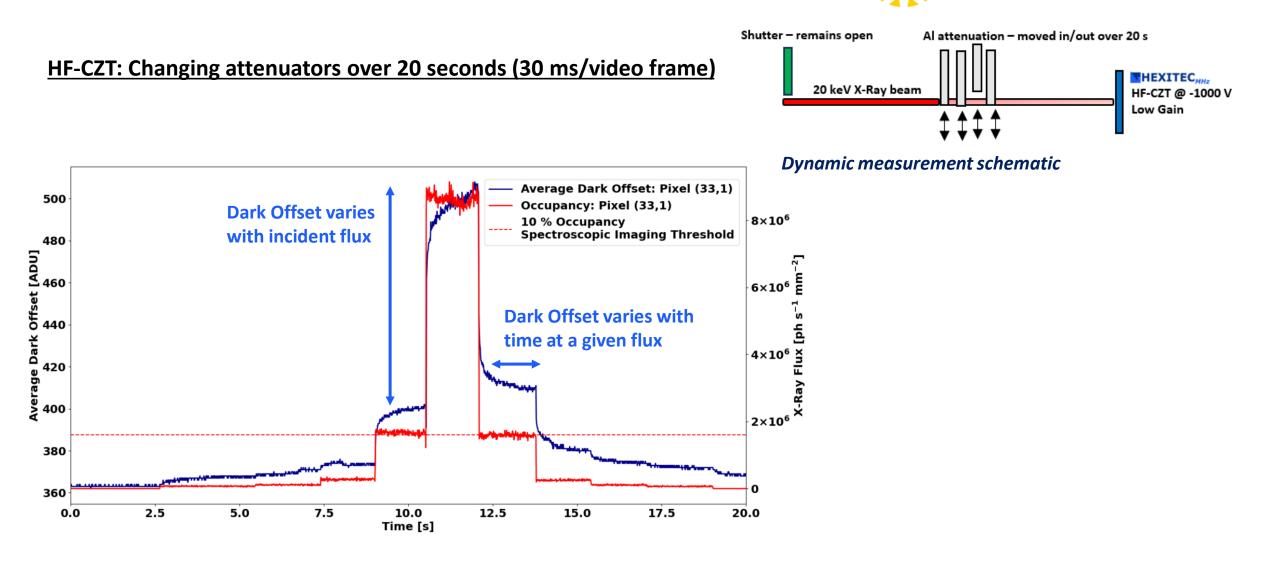

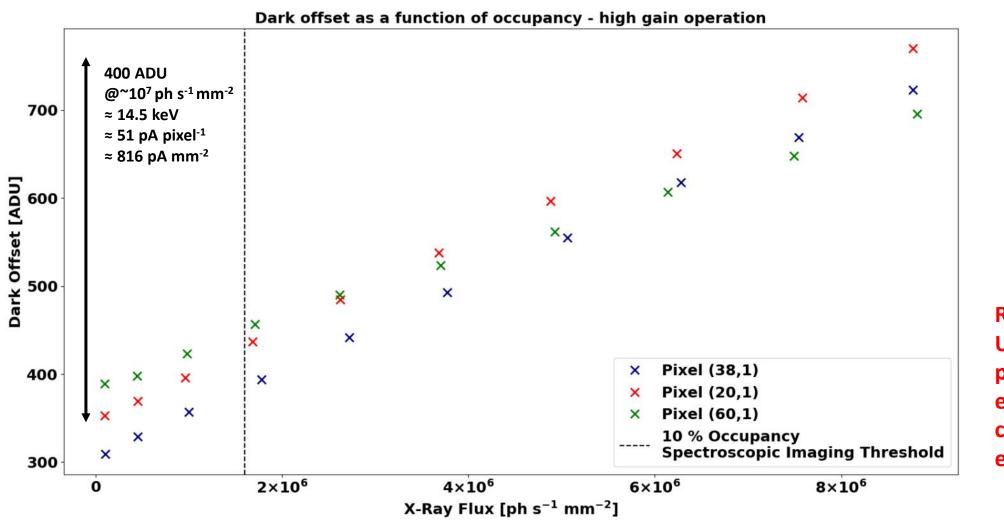

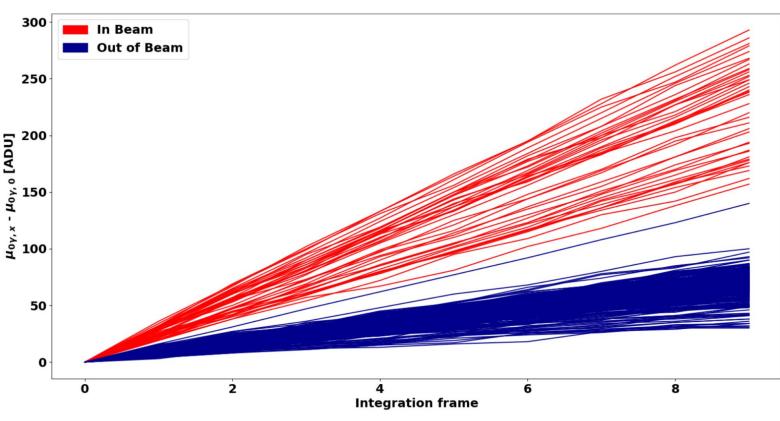

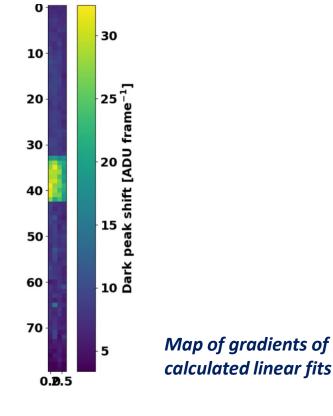

# HF-CZT Offset: Dynamic Datasets at diamond

Dynamic measurement schematic

# HF-CZT Offset: Dynamic Datasets at diamond

HF-CZT detector @ -1000 V @ 20 keV: Variation of dark offset with X-Ray flux

Real time Xilinx U50 FPGA processing will enable live corrections of this effect

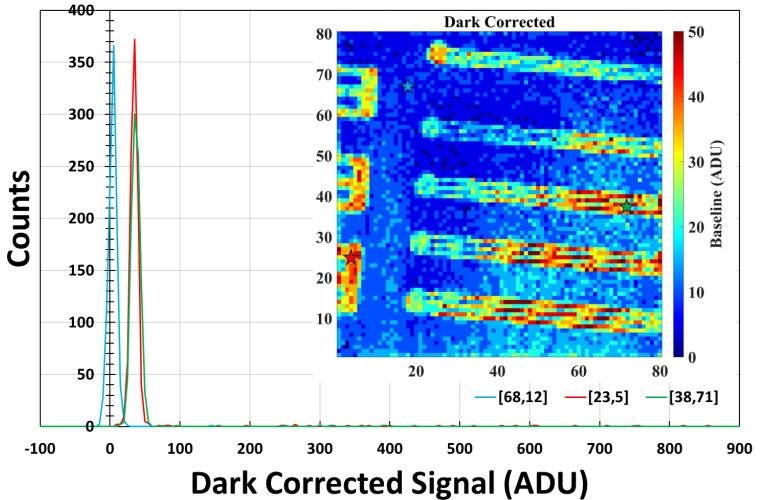

## **HF-CZT offset: Area scans in laboratory**

A lead line pair per mm slide placed over the HF-CZT sensor

Histograms of signals measured in three pixels from different areas in the irradiation showing different offsets. (Inset) A map of dark-offset

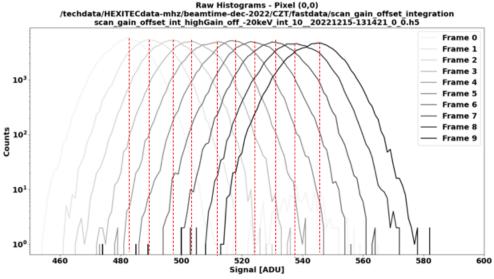

#### **1.** Impede CSA reset ( $S_{CSA}$ ) for 10 $\mu$ s

ASIC continues outputting every 1 μs

#### **2.** Group and histogram all related frames

• E.g. all 1R frames (1 frame following reset)

| 0          | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

|------------|----|----|----|----|----|----|----|----|----|

| Reset – OR | 1R | 2R | 3R | 4R | 5R | 6R | 7R | 8R | 9R |

| 10         | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| Reset – OR | 1R | 2R | 3R | 4R | 5R | 6R | 7R | 8R | 9R |

| 20         | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| Reset – OR | 1R | 2R | 3R | 4R | 5R | 6R | 7R | 8R | 9R |

#### Schematic of frames outputted utilising a 10 µs reset length

#### 3. Identify dark offset for each frame type

Shifts to higher ADU as integrating Front-End

#### Raw Histograms - Pixel (0,0) Dark Signal Shift - Pixel (0,0) /techdata/HEXITECdata-mhz/beamtime-dec-2022/CZT/fastdata/scan gain offset integration /techdata/HEXITECdata-mhz/beamtime-dec-2022/CZT/fastdata/scan gain offset integration scan gain offset int highGain off -20keV int 10 20221215-131421 0 0.h5 scan gain offset int highGain off -20keV int 10 20221215-131421 0 0.h5 Frame 0 y = 6.85x + -0.15Frame 1 60 Frame 2 Frame 3 10<sup>3</sup> Frame 4 50 Frame 5 [NDV] 40 Frame 6 Frame 7 Shift Frame 8 10<sup>2</sup> Frame 9 Signal 80 ₹ 20 10<sup>1</sup> Da 10 100 500 540 460 480 520 560 580 600 2 4 6 8 Signal [ADU] Integration frame

Identification of dark offset for each histogram

*Linear-fit calculation to a plot of dark offset vs frames following reset*

4. Calculate linear fit to dark offset vs frames following reset

**Provides measure of pixel's leakage current**

Outside of beam – Pixel (0,0) Fit gradient - 6.85 ADU frame<sup>-1</sup>

- $\rightarrow$  Leakage current = 8.5 pA (136 pA mm<sup>-2</sup>)

- Typical value for the leakage current

- Inside of beam Pixel (40,2) Fit gradient – 23.87 ADU frame<sup>-1</sup>

- $\rightarrow$  Leakage current = 31.2 pA (500 pA mm<sup>-2</sup>)

- This is a ~24 pA higher than outside of the beam

## Agenda

## **1 HEXITEC vs HEXITEC**<sub>MHz</sub>

The next generation of HEXITEC systems

## 2 HEXITEC<sub>MHz</sub> Overview

An introduction to our new  $\text{HEXITEC}_{\text{MHz}}$  ASIC including its architecture and specification

### **3 HF-CZT Test Results**

Characterisation of spectroscopic performance using a labbased X-Ray source and Diamond Light Source synchrotron X-Rays

### **4 Next Steps**

A look to the next 12 months

## **Next Steps**

#### Achieving a 20-channel fast data output

• Reading out the full 80 × 80 array using the fast data

Further lab-based ASIC and HF-CZT characterisation

- Performance variation across entire active area

- Continued study of observed offset effect

Implementation of in-FPGA histogramming

- Orders of magnitude reduction in output data

- Live correction of observed offset effect

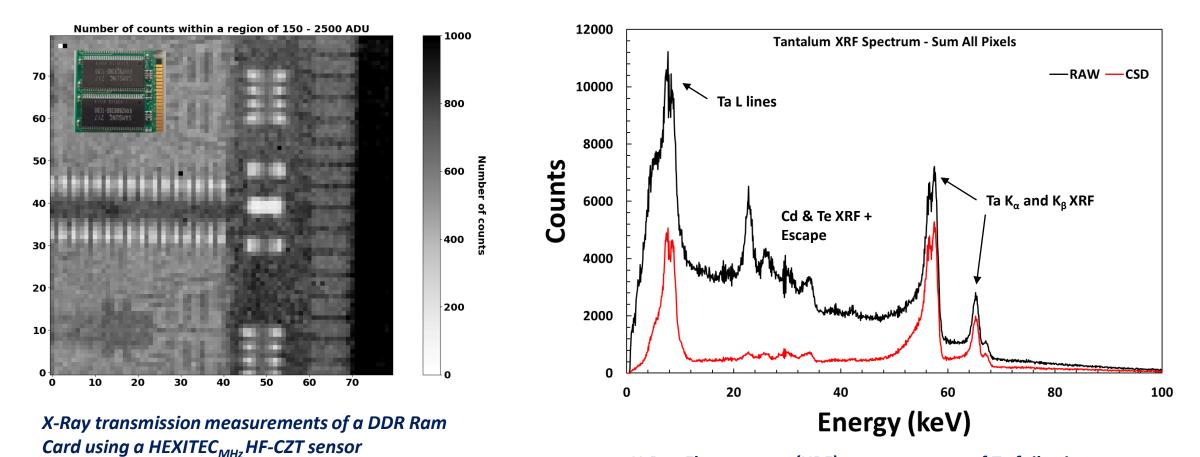

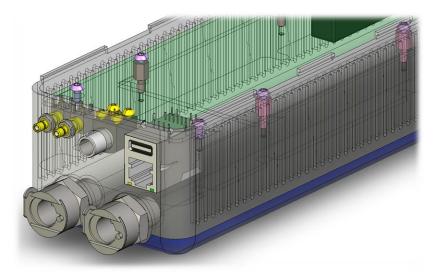

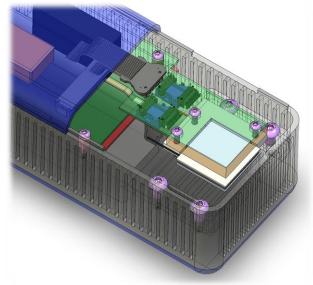

Delivery of HEXITEC<sub>MHz</sub> detector system

• Smaller, form factor production-grade system

#### **Delivering Science**

Possible designs for HEXITEC<sub>MHz</sub> detector system

• HEXITEC<sub>MHz</sub> is a fully-spectroscopic X-Ray detector capable of operating continuously at 1 MHz

| Parameter                                                     | HEXITEC <sub>MHz</sub>                                        |

|---------------------------------------------------------------|---------------------------------------------------------------|

| Max Frame Rate (MHz)                                          | 1                                                             |

| Max Spectroscopic Flux (ph s <sup>-1</sup> mm <sup>-2</sup> ) | >10 <sup>6</sup>                                              |

| Digitisation                                                  | On-chip                                                       |

| Detector Type                                                 | Integrating                                                   |

| Measured FWHM (High Gain)                                     | 0.85 keV @ 20 keV in HF-CZT<br>0.68 keV @ 15 keV in p-type Si |

- The next year will include delivery of a full  $80 \times 80$  pixel readout and a new smaller form-factor system

- HEXITEC<sub>MHz</sub> has been used to observe and investigate a flux-dependent dark offset within Redlen HF-CZT

- Investigation into this phenomenon is continuing.

If you have any further questions, please contact me at: <a href="mailto:ben.cline@stfc.ac.uk">ben.cline@stfc.ac.uk</a>

## **Backup Slides**

# **Testing – Test Setup**

*HEXITEC*<sub>*MHz</sub>test enclosure* (*interior*)</sub>

*HEXITEC*<sub>MHz</sub> test enclosure (exterior)

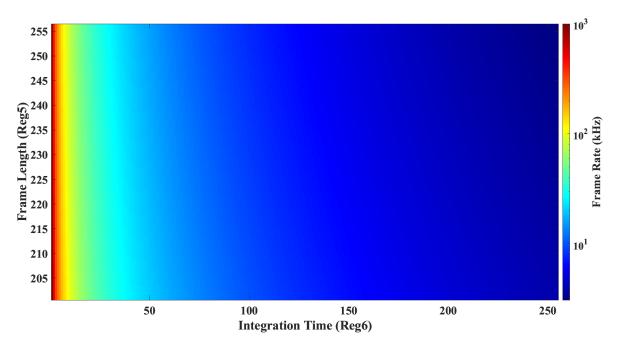

# **Available Frame Rates**

• Two chip registers can be altered:

٠

- Frame Time: **200** $\rightarrow$ 255 clocks frame<sup>-1</sup>

- Integration Length:  $1 \rightarrow 255$  frames

**Default values**

## Available Frame Rates

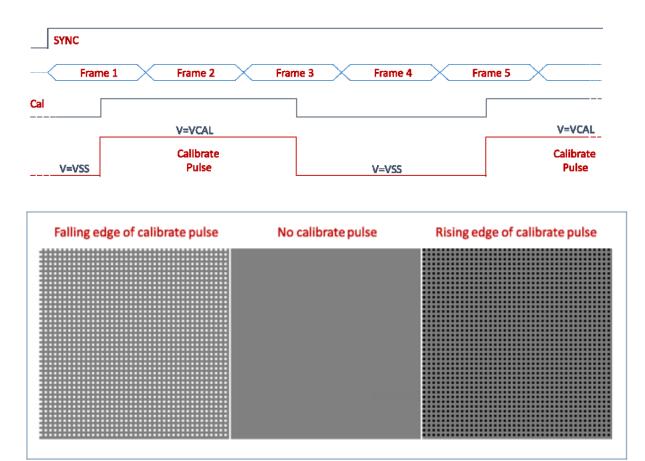

## **Test Pulse Sequence**

### Test pulse sequence

## **Front End – Negative Offset Circuit**

Negative offset circuit

Science and Technology Facilities Council

## **Data Output Plane**

Data output path schematic

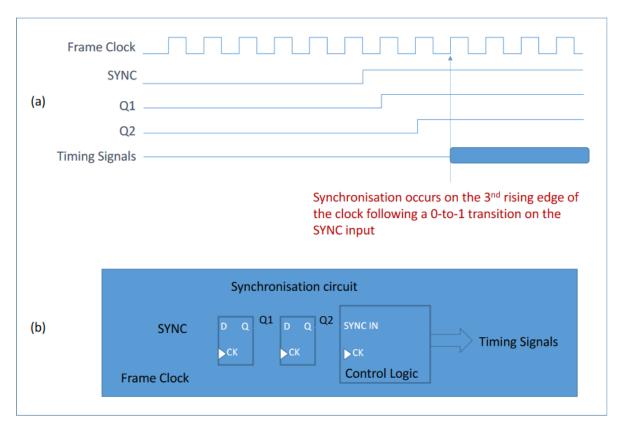

## Synchronising the ASIC

Synchronisation circuit

Science and Technology Facilities Council

- ASIC synchronised by controlling transition of SYNC input

- Logic  $0 \rightarrow \text{logic } 1$

- Synchronisation occurs on 3<sup>rd</sup> subsequent rising clock edge

- Used for external synchronisation and multi-ASIC systems

## **Electronic Noise Contribution**

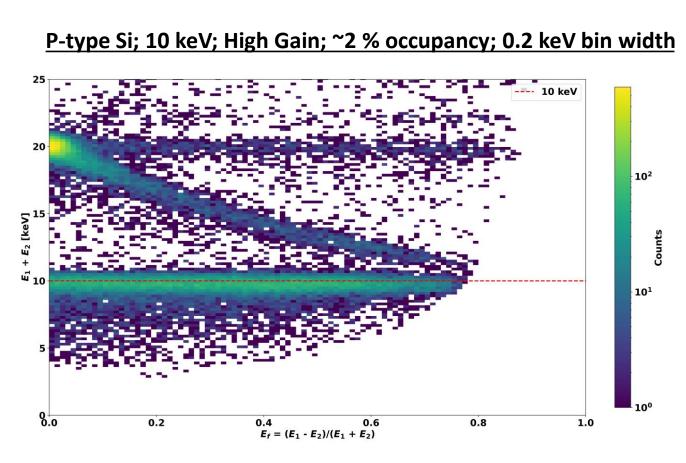

The distribution of energies in two-pixel charge sharing events using a 10 keV beam energy at an occupancy of ~2% - 0.2 keV bin width

HF – CdZnTe Frame occupancy: 0.4%

#### Open Access Article

## Charge Sharing and Charge Loss in High-Flux Capable Pixelated CdZnTe Detectors

by 😵 Kjell A. L. Koch-Mehrin 1.\* ⊠, 😰 Sarah L. Bugby 2 ⊠ 🥯, 😩 John E. Lees 1 ⊠ 🧐, 😩 Matthew C. Veale <sup>3</sup> ⊠ 😳 and இ Matthew D. Wilson <sup>3</sup> ⊠

<sup>1</sup> Space Research Centre, Department of Physics & Astronomy, University of Leicester, Leicester LE1 7RH, UK

- <sup>2</sup> Centre for Imaging Science, Department of Physics, Loughborough University, Loughborough LE11 3TU, UK

- <sup>3</sup> STFC Rutherford Appleton Laboratory, Harwell Campus, Didcot OX11 0QX, UK

- \* Author to whom correspondence should be addressed.

Sensors 2021, 21(9), 3260; https://doi.org/10.3390/s21093260

Received: 31 March 2021 / Revised: 26 April 2021 / Accepted: 6 May 2021 / Published: 8 May 2021

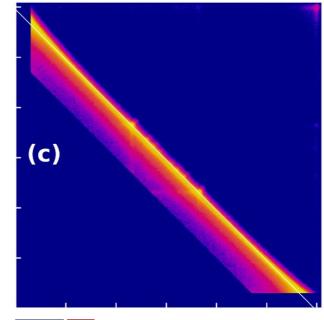

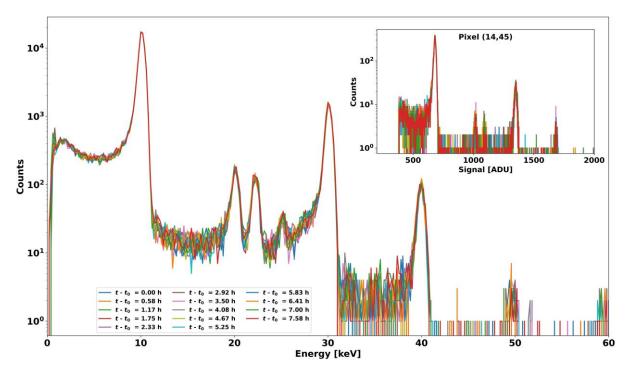

# diamond – Temporal Stability

Evolution of high-gain calibrated global CSD spectra during exposure @ 10 keV for ~8 h – 0.2 keV bin width. Inset plot shows uncalibrated CSD spectra for pixel (14,45) – 1 ADU bin width

Change in performance of p-type  $\text{HEXITEC}_{\text{MHz}}$  device during exposure @ 10 keV for ~8 h. Plots show fluctuation in peak position (a), change in FWHM (b), and fractional change in peak counts (c) of 10 keV photo peak. Peak counts comprise events within the FWHM of peak, and error bars given by standard deviation across beam region

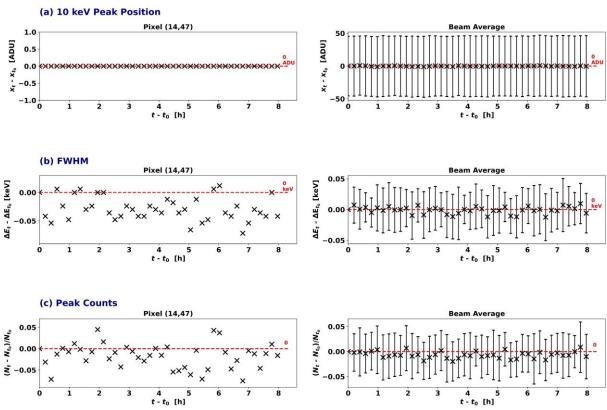

# **TSVs on HEXITEC**

(a) I/O pads on reverse of the 200 mm HEXITEC4S wafer post-TSV-last processing. (b) RDL pads dimensions on ASIC's reverse. (c) SEM micrograph of exposed TSVs in cleaved test chip. (d) SEM micrograph showing contact between TSV and ASIC's bottom metal layer

Science and Technology Facilities Council

## https://doi.org/10.1016/j.nima.2021.166083

Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment Volume 1025, 11 February 2022, 166083 A A CARACTERIA CONTRACTOR CONTRAC

## Characterisation of the HEXITEC<sub>4S</sub> X-ray spectroscopic imaging detector incorporating through-silicon via (TSV) technology

M.C. Veale<sup>a</sup> or the source of the source of

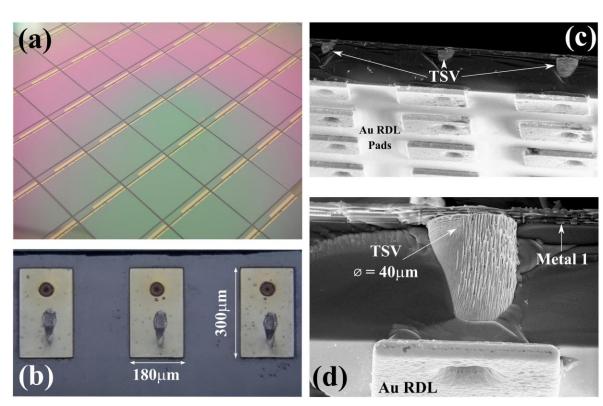

Wafer maps showing results of probe testing. Green – functioning; Red – non-functioning

# Next steps – Current Applications

**MIC-12-434:** On the feasibility of using HEXITEC<sub>MHZ</sub> and fullyspectral x-ray imaging to detect breast tumours: an in-silico study

The ROYAL MARSDEN NHS Foundation Trust R The Institute of Cancer Research

**New Project:** 5DCT – *Dynamic Colour X-ray Computed Tomography*

National X-Ray Computed Tomography

弦

Biotechnology and Biological Sciences Research Council

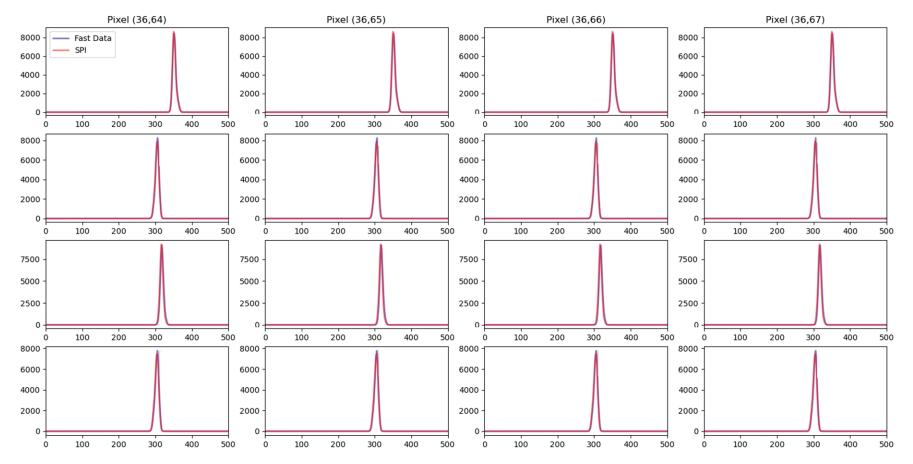

## **Testing – SPI vs Fast Data Comparison**

Comparison of fast data and SPI measurements using test pulse

Fast data matches SPI output ©